The Serial Port & P.C.Arnold Technical Services Present

# The PCATS Graphics Enhancer

Release 1 00

The Serial Port Burcott Manor, Wells, Somerset BA5 1NH Tel: 0243 531194 Fax: 0243 531196

#### The Serial Port Copyright Policy

At The Serial Port we believe that whenever possible our software should NOT be copy protected, thus allowing you to easily make back-up copies of the software or run it from a hard disk. We do sometimes have to make exceptions to this rule but the decision to protect *a* program is not taken without a great deal of thought going into finding alternative methods to protect our copyright.

This means we are placing a great deal of trust, and our future as a software supplier, in your hands. We ask you not to abuse your position - by all means recommend and demonstrate our software to friends, but **please** do not give them a copy. If you do you will be doing harm to everybody, including yourself, as we will no longer be able to supply improved versions of our software at low cost to present users such as yourself or invest in new projects which will help increase the Archimedes user base - you wouldn't want to force us to go and program IBM PC's, would you?

We have every faith in our users and believe that we can safely supply our software in this unprotected form. Help us to help you - Spread the word, not the disk!

Hardware © 1990/1991 Patrick Arnold Software © 1990/1991 Patrick Amold/Hugo Fiennes/The Serial Port

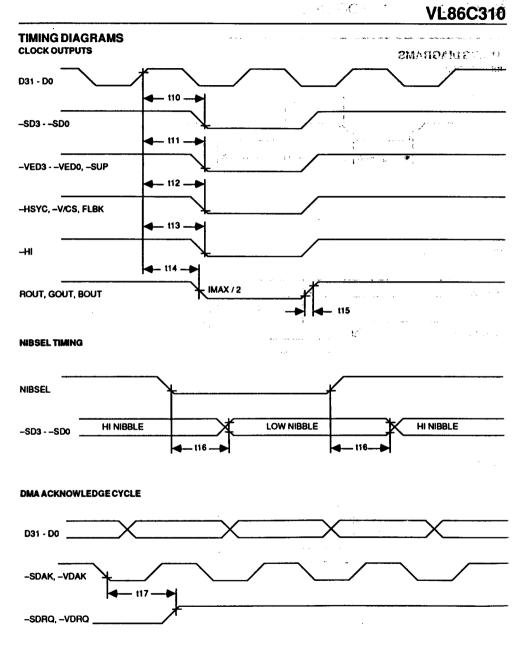

VL86C310 data sheet © VLSI Technology [nc., San Jose, California, USA. Reprint by permission.

<u>PLEASE NOTE:</u> The ColourTrans V0.70 module supplied with this product Is based upon original code licensed from Acorn Computers Ltd. [t has been tested and found to work with a large majority of the commercial software available at the time of printing of this manual, but cannot be absolutely guaranteed to work with all software which will be written for RISC OS. [f and when new versions of RISC OS are released, the version of ColourTrans supplied with them should be used in place of the version supplied on the Graphics Enhancer utilities disk.

N0 part of this manual (except for brief passages qu0ted f0r critical purp0ses) or 0f the c0mputer pr0grams t0 which it relates, may be reproduced, transmitted or translated in any f0rm 0r by any means, electronic, mechanical 0r 0therwise, without the pri0r c0nsent 0f the copyright owner.

The Graphics Enhancer is a complex product which is under continu0us development and, while every effort is made to ensure it functions as detailed, neither The Serial POrt nor Acom can accept any liability for any loss or damage resulting from the use The Graphics Enhancer or the information in this manual.

All trademarks used in this manual are ackn0wledged

Page II

# Contents

| Introduction                                                       | 1   |

|--------------------------------------------------------------------|-----|

| Why you need a Graphics Enhancer                                   | 3   |

| * Commands                                                         | 5   |

| Graphics Enhancer SWI calls                                        | 35  |

| APPENDIX A: CLEAR file format                                      | 74  |

| APPENDIX B: Class P TIFF file format                               | 75  |

| APPENDIX C: Using the 12 BPP & 16 BPP modes                        | 78  |

| APPENDIX D: Mode Description Language                              | 80  |

| APPENDIX E: Error Messages                                         | 83  |

| APPENDIX F: Installation of Graphics Enhancer                      | 85  |

| Installation procedure for 300 series, 400 & 400/1 series, and 540 | 85  |

| Installation procedure for A3000                                   | 86  |

| Configuration of Graphics Enhancer after Installation              | 86  |

| APPENDIX G: Currently defined screen modes                         | 87  |

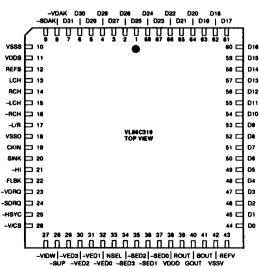

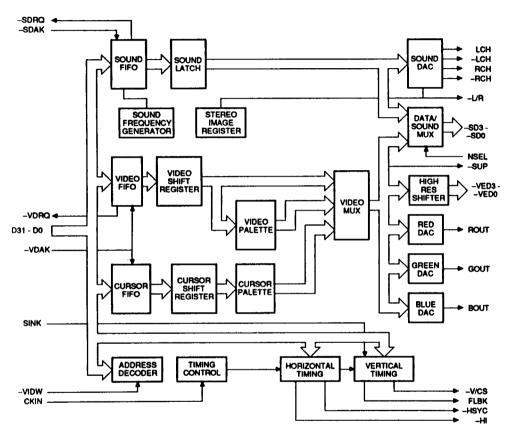

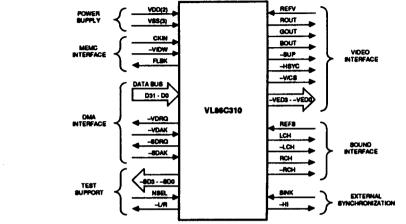

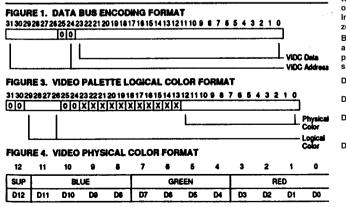

| APPENDIX H: VL86C310 data sheet                                    | 92  |

| Index                                                              | 113 |

#### Introduction

The PCATS Graphics Enhancer, marketed by The Serial Port, is an expansion card for the Acorn Archimedes range of microcomputers. It is designed as a low-cost, high performance upgrade for significantly improving the graphics performance of these machines. Coupled with the high speed and versatile architecture of the Archimedes, it can produce results *as* good as, if not better than, some professional CAD type workstations, at a far lower cost.

The Graphics Enhancer will work with any machine in the Archimedes range, from an A3000 to a 540. On the 310, 400 & 400/1 series, and the 540, it plugs into the podule expansion backplane, inside the machine. On the A3000, it fits externally onto the rear expansion connector, and requires a small adaptor board which fits over the VIDC chip inside the computer case.

The enhancements provided by the board can be grouped into five main areas, as follows:

(1) A 24-bit palette, giving 256 colours on screen simultaneously, selectable from 16,777,216 available colours. This feature allows modes with resolutions of up to 768 x 288 on a standard monitor, and resolutions of 832 x 328, 512 x 512, 640 x 480, & others on a multisync monitor. These modes all work correctly with the Desktop, and the new version of the ColourTrans module supplied will allow any properly written Desktop application to work in them.

(2) 12 bpp direct DAC modes, giving 4096 simultaneous colours, at resolutions of up to 512 x 288 on a standard monitor, and up to 554 x 328 on a multisync monitor. These modes are not Desktop compatible.

(3) 16 bpp direct DAC modes, giving 65536 simultaneous colours, at resolutions of up to  $384 \times 288$  on a standard monitor, and up to  $416 \times 328$  on a multisync monitor. These modes are not Desktop compatible.

(4) A set of up to seven VIDC clocks, software selectable by \* commands or SWI calls. The clocks installed as standard are 24 MHz, 25.175 MHz, 32 MHz, & 36 MHz. There are 3 empty sockets on the Graphics Enhancer board, which can have user-supplied oscillators plugged into them. The Serial Port can supply oscillator modules for any frequency required. VLSI specifications give the maximum operating speed of the VIDC as 36 MHz, but we have found that most will work to 40 MHz, and some to as high as 48 MHz. However, we cannot guarantee that any particular VIDC will work above 36 MHz. We can supply oscillators of any frequency required, and we also produce a Mode Booster upgrade board, which is necessary for the Graphics Enhancer itself to run faster than 36 MHz. Contact The Serial Port for prices.

(5) The ability to define new modes as text files, using the Mode Description Language compiler supplied with the Graphics Enhancer. This will allow the user to make new modes at will, utilising all the extra video facilities that are provided by the hardware.

The Graphics Enhancer also adds many other new modes, including all those provided by the Computer Concepts mode module (supplied with Impression), all those provided by the Atomwide VIDC enhancer, and the new Super VGA modes as used on the 540. See Appendix G for a full list of defined modes.

Software support for the various features of the Graphics Enhancer is quite extensive, with many SWI calls and \* commands. Several major software houses are now, or will soon be, adding features to their graphics-based programs to take full advantage of the new modes added to the standard Archimedes.

A Professional version of the Graphics Enhancer will soon be available, which will add full genlock capability to the other features supported by the standard version, allowing any of the 256 Desktop colours to have up to 24 bits of overlay keying, independently of the rest. Please contact The Serial Port for pricing and availability.

#### Why you need a Graphics Enhancer

The Acorn Archimedes computers are probably the fastest, easiest to use, and most programmable microcomputers available in their price range, or anywhere close to it. However, in one key area they lag behind other machines, such as the Apple Macintosh. That area *is* the quality of onscreen pictures. The graphics of the Archimedes are very fast, and much better than many machines can produce at two or three times the price. but have some fairly severe limitations, notably in the number and range of colours that are available.

In 256 colour modes, the Archimedes is quoted as having a palette of 4096 colours, implying that any 256 of these can be used at any one time. In fact, due to the somewhat peculiar way the video hardware is designed, colours can only be chosen in blocks of 16, which almost inevitably gives one colour that is very nearly, but not quite, the one required, and 15 others that are nowhere near it. Even given these limitations, the results that can be obtained are amazing. However, it would be nice to have a true palette, with any of the 256 colours independently selectable from a larger range than in normally available.

This is precisely what the Graphics Enhancer does.

It allows 256 totally independent colours to be selected from a range of over 16.7 million, thus ensuring that whatever colour is wanted can be obtained. In most applications, 256 colours are sufficient, given that there is a large enough selection to pick from. Even so, there are times when more colours are needed onscreen simultaneously. In these cases, the Graphics Enhancer can also help, as it has 12 and 16 bpp modes, giving up to 65536 colours at once. Unfortunately, the current version of RISC OS cannot handle more than 8 bits per pixel, so these modes can only be used by programs written specifically for them.

The extended palette modes are fully supported by the operating system. Simple BASIC programs can easily take advantage of the extended range of available colours, thus allowing anyone with a modicum of programming knowledge to obtain spectacular results. For non-programmers, the Graphics Enhancer is being supported by several software houses, who are adding support for it to their RISC OS applications.

In addition to adding the facility of more and better colours, the Graphics Enhancer also allows the VIDC to be run at different frequencies than the default 24 MHz, thus allowing higher resolution modes, although only in 16 colours. It is fully compatible with the Atomwide VIDC enhancer, which means that people who have written programs using the various Atomwide modes can continue to use them when the Graphics Enhancer is installed. It also adds all the modes that are supported by the Computer Concepts Impression mode module, and those that are new to the A540. A full list of the modes that are supported as standard by the Graphics Enhancer can be found in Appendix G. In addition, new modes can be defined as text files, which are then compiled using the supplied program !MDLcomp to a 200 byte mode descriptor data block. Up to 36 of these data blocks can be loaded at once, taking up a mere 7400 bytes of RMA.

Page 3

The Graphics Enhancer is totally transparent in operation, needing no special commands to turn it on or off. Any program that uses its extended graphics facilities will use it, and any program that does not use it will simply ignore it. As a result, there is very little in the way of user instructions needed, except for programming information for those who wish to write programs for the extended palette modes, etc. The manual that follows lists all the new \* commands and SWI's that the Graphics Enhancer software provides, along with information on using the 12 & 16 bpp modes, on the CLEAR & TIFF file formats that are used for saving extended palette screens, and technical information on the VIDC chip itself. If the user does not wish to write programs using the new graphics facilities, much of this manual can simply be ignored. The section on configuration commands, at the end of the \* command list, should be read by all users, as it can help if there are problems in the operation of the Graphics Enhancer. Such problems are almost inevitably due to one or more of the \*Configure options being set wrongly.

Any comments or suggestions for changes to this manual or the Graphics Enhancer software are welcomed, and should be sent to The Serial Port. If you have any special project that requires technical information not given in this manual, please let us know and we will try to help.

# \* Commands

| *VIDC          | Programs VIDC registers directly.                               |

|----------------|-----------------------------------------------------------------|

| *Clock         | Sets or reads the VIDC clock rate.                              |

| *Dac           | Enables 12 or 16 bpp direct DAC mode.                           |

| *ExtPal        | Enables 24-bit extended palette mode.                           |

| *Default       | Restores default Graphics Enhancer settings.                    |

| *NormalVideo   | Restores default Archimedes video output.                       |

| *Pmask         | Programs pixel mask.                                            |

| *Palette       | Programs extended palette.                                      |

| *Mode          | Sets screen mode.                                               |

| *PalSet        | Sets red scale/restores default palette.                        |

| *DeskPal       | Sets Desktop equivalent palette in extended palette modes.      |

| *PalSave       | Saves the current extended palette.                             |

| *PalLoad       | Loads an extended palette file.                                 |

| *ClearSave     | Saves the current extended palette mode screen as a CLEAR file. |

| *ClearLoad     | Loads a CLEAR file to the screen.                               |

| *GreyScale     | Sets the extended palette to a linear greyscale.                |

| *Gcol          | Sets graphics colour in extended palette modes.                 |

| *Colour        | Sets text colour in extended palette modes.                     |

| *LinkMode      | Loads a mode definition file and links it in as a screen mode.  |

| *LinkModeClear | Clears all linked modes.                                        |

| *DeLinkMode    | Delinks an individual linked mode.                              |

- \*Configure CrystalSlots

- \*Configure DefaultCrystal

- \*Configure ProcessorType

- \*Configure MonitorGroup

- \*Configure IREThreshold

- \*Configure TurboModes

- Configures occupied VIDC oscillator sockets.

- Configures default VIDC clock.

- Configures installed processor type.

- Configures group of attached monitor.

- Configures blanking level of monitor.

- Configures optional mode booster enable/disable.

#### **\*VIDC**

|                        | Programs VIDC registers directly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| Syntax                 | *VIDC <register> <value< th=""><th>&gt;</th></value<></register>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | >                                                        |  |

| Parameters             | <register> is a valid VID0<br/><value> is a number with</value></register>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C register<br>in the range allowed for the VIDC register |  |

| Use                    | *VIDC allows direct programming of VIDC registers from the command<br>line. This can be useful for experimenting with new values for creating<br>new modes, without having to create a mode definition module.<br>However, Risc-OS will not know about the new values, so the VDU<br>drivers will not correctly handle the changes. See Appendix H for more<br>details of register numbers and allowed values.<br><u>Warning!</u> Use this command with caution, as programming<br>the VIDC with the wrong values could damage your monitor. |                                                          |  |

| Example                | *VIDC &A0 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sets the VCR to 312 rasters                              |  |

| Related commands       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |  |

| Related SWIs           | Enhancer_VIDC (SWI &42A55)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |  |

| <b>Related vectors</b> | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |  |

## \*Clock

|                        | Sets or reads the VIDC clock rate                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax                 | *Clock [ <n>]</n>                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Parameters             | [ <n>] is a number between 0 and 7</n>                                                                                                                                                                                                                                                                                                                                    |  |  |

| Use                    | *Clock connects the oscillator in socket <n> to the VIDC. The default clock frequencies and the socket numbers are as follows:</n>                                                                                                                                                                                                                                        |  |  |

|                        | Socket 0: 24 MHz<br>1: 25.175 MHz<br>2: 32 MHz<br>3: 36 MHz<br>4: empty (for user-supplied oscillator)<br>5: empty (for user-supplied oscillator)<br>6: empty (for user-supplied oscillator)<br>7: 24 MHz<br>Only sockets that have been marked as occupied by *Configure<br>CrystalSockets can be selected. *Clock with no parameter will<br>return the current setting. |  |  |

| Example                | *Clock 2 Sets the VIDC clock rate to 32 MHz                                                                                                                                                                                                                                                                                                                               |  |  |

| Related commands       | *Configure CrystalSockets                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Related SWIs           | Enhancer_Clock (SWI &42A4C)                                                                                                                                                                                                                                                                                                                                               |  |  |

| <b>Related vectors</b> | None                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                        | Enables 12 or 16 bpp direct DAC mode                                                                                                                                           |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax                 | *Dac <bpp></bpp>                                                                                                                                                               |  |  |

| Parameters             | <br>s either 12 or 16                                                                                                                                                          |  |  |

| Use                    | *Dac is used to force the Graphics Enhancer to either 12 or 16 bpp direct DAC mode. The Graphics Enhancer software transparently does this when displaying 12 or 16 bpp modes. |  |  |

| Example                | *Dac 12 Sets 12 bpp mode                                                                                                                                                       |  |  |

| Related commands       | *ExtPal                                                                                                                                                                        |  |  |

| Related SWIs           | Enhancer_Dac (SWI &42A4B)<br>Enhancer_ExtPalette (SWI &42A4A)                                                                                                                  |  |  |

| <b>Related vectors</b> | None                                                                                                                                                                           |  |  |

#### \*ExtPal

|                        | Enables 24-bit extended palette mode                                                                                                                                         |                          |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Syntax                 | *ExtPal                                                                                                                                                                      |                          |

| Parameters             | None                                                                                                                                                                         |                          |

| Use                    | *ExtPal is used to force the Graphics Enhancer to 24-bit extended<br>palette mode. The Graphics Enhancer software transparently does this<br>when in extended palette modes. |                          |

| Example                | *ExtPal                                                                                                                                                                      | Enables extended palette |

| Related commands       | *Dac                                                                                                                                                                         |                          |

| Related SWIs           | Enhancer_Dac (SWI &42A4B)<br>Enhancer_ExtPalette (SWI &42A4A)                                                                                                                |                          |

| <b>Related vectors</b> | None                                                                                                                                                                         |                          |

## \*Default

#### Restores default Graphics Enhancer settings

| Syntax                 | *Default                                                                                                      |                         |

|------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| Parameters             | None                                                                                                          |                         |

| Use                    | *Default is used to reset the Graphics Enhancer to normal Archimedes video output and 24 MHz VIDC clock rate. |                         |

| Example                | *Default                                                                                                      | Reset Graphics Enhancer |

| Related commands       | *Normal Video                                                                                                 |                         |

| Related SWIs           | Enhancer_Default (SWI &42A46)<br>Enhancer_NormalVideo (SWI &42A47)                                            |                         |

| <b>Related vectors</b> | None                                                                                                          |                         |

## \*NormalVideo

|                  | Restores default Archimedes video output                                                                                         |                                        |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Syntax           | *NormalVideo                                                                                                                     |                                        |  |

| Parameters       | None                                                                                                                             |                                        |  |

| Use              | *NormalVideo is used to reset the Graphics Enhancer to normal<br>Archimedes video output, without affecting the VIDC clock rate. |                                        |  |

| Example          | *NormalVideo                                                                                                                     | Restore normal Archimedes video output |  |

| Related commands | *Default                                                                                                                         |                                        |  |

| Related SWIs     | Enhancer_Default (SWI &42A46)<br>Enhancer_NormalVideo (SWI &42A47)                                                               |                                        |  |

| Related vectors  | None                                                                                                                             |                                        |  |

#### \*Pmask

#### Programs pixel mask

| Syntax           | *Pmask [ <n>]</n>                                                                               |                        |  |

|------------------|-------------------------------------------------------------------------------------------------|------------------------|--|

| Parameters       | [ <n>] is a number between 0 and 255</n>                                                        |                        |  |

| Use              | *Pmask is used to write the pixel mask. *Pmask with no parameter prints the current pixel mask. |                        |  |

| Example          | *Pmask 255                                                                                      | Set the pixel mask off |  |

| Related commands | None                                                                                            |                        |  |

| Related SWIs     | Enhancer_PixelMaskWrite (SWI &42A44)<br>Enhancer_PixelMaskRead (SWI &42A45)                     |                        |  |

| Related vectors  | None                                                                                            |                        |  |

#### \*Palette

|                  | Programs extended palette                                                                                                                                                        |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax           | *Palette <c> <r> <g> <b></b></g></r></c>                                                                                                                                         |  |  |

| Parameters       | <c> is an 8-bit colour number<br/><r> is an 8-bit red component value<br/><g> is an 8-bit green component value<br/><b> is an 8-bit blue component value</b></g></r></c>         |  |  |

| Use              | *Palette is used to program individual extended palette entries.<br>Please note that colour 0 cannot be programmed to other than black,<br>for various hardware-related reasons. |  |  |

| Example          | *Palette 100 255 0 0 Sets colour 100 to full red, no green, and no blue                                                                                                          |  |  |

| Related commands | None                                                                                                                                                                             |  |  |

| Related SWIs     | Enhancer_PaletteBlockWrite (SWI &42A40)<br>Enhancer_PaletteBlockRead (SWI &42A41)<br>Enhancer_PaletteWrite (SWI &42A42)<br>Enhancer_PaletteRead (SWI &42A43)                     |  |  |

| Related vectors  | None                                                                                                                                                                             |  |  |

#### \*Mode

|                        | Sets screen mode                                                                                         |              |  |

|------------------------|----------------------------------------------------------------------------------------------------------|--------------|--|

| Syntax                 | *Mode [ <n>]</n>                                                                                         |              |  |

| Parameters             | [ <n>] is any valid mode number</n>                                                                      |              |  |

| Use                    | *Mode is an exact equivalent of the BASIC MODE command. *Mode with no parameter prints the current mode. |              |  |

| Example                | *Mode 12                                                                                                 | Sets mode 12 |  |

| Related commands       | None                                                                                                     |              |  |

| Related SWIs           | None                                                                                                     |              |  |

| <b>Related vectors</b> | None                                                                                                     |              |  |

|                        | Sets red scale/restores default palette                                                                                                                                                                      |                       |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| Syntax                 | *PalSet <0 1>                                                                                                                                                                                                |                       |  |

| Parameters             | <0 1> is 0 for default Archimedes palette, or 1 for red scale                                                                                                                                                |                       |  |

| Use                    | *PalSet is used to set a linear red scale in 4 bpp modes, or to restore the default palette. If $\langle n \rangle$ is 1, the palette is set to a red scale, and if it is 0 the default palette is restored. |                       |  |

| Example                | *PalSet 1                                                                                                                                                                                                    | Sets linear red scale |  |

| Related commands       | None                                                                                                                                                                                                         |                       |  |

| <b>Related SWIs</b>    | Enhancer_PalSet (SWI &42A49)                                                                                                                                                                                 |                       |  |

| <b>Related vectors</b> | None                                                                                                                                                                                                         |                       |  |

#### \*DeskPal

#### Sets Desktop equivalent palette in extended palette modes

| Syntax                 | *DeskPal                                                                                                    |                               |

|------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------|

| Parameters             | None                                                                                                        |                               |

| Use                    | *DeskPal is used to set the palette in extended palette modes to an equivalent of the standard desktop one. |                               |

| Example                | *DeskPal                                                                                                    | Sets standard desktop palette |

| Related commands       | None                                                                                                        |                               |

| <b>Related SWIs</b>    | Enhancer_SetDesktopPalette (SWI &42A4E)                                                                     |                               |

| <b>Related vectors</b> | None                                                                                                        |                               |

#### \*PalSave

|                        | Saves the current extended                                                                         | ed palette                         |

|------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|

| Syntax                 | *PalSave <filename></filename>                                                                     |                                    |

| Parameters             | <filename> is any valid filename</filename>                                                        |                                    |

| Use                    | *PalSave is used to save the current extended palette as a palette file with the filetype of &C8A. |                                    |

| Example                | *PalSave palfile                                                                                   | Saves current palette as "palfile" |

| Related commands       | *PalLoad                                                                                           |                                    |

| Related SWIs           | Enhancer_PaletteSave (SWI &42A52)<br>Enhancer_PaletteLoad (SW! &42A53)                             |                                    |

| <b>Related vectors</b> | None                                                                                               |                                    |

#### \*PalLoad

#### Loads an extended palette file

| Syntax                 | *PalLoad <filename></filename>                                                              |                                       |  |

|------------------------|---------------------------------------------------------------------------------------------|---------------------------------------|--|

| Parameters             | <filename> is any valid filename</filename>                                                 |                                       |  |

| Use                    | *PalLoad is used to load an extended palette file and make it the current extended palette. |                                       |  |

| Example                | *PalLoad palfile                                                                            | Loads extended palette file "palfile" |  |

| Related commands       | *PalSave                                                                                    |                                       |  |

| Related SWIs           | Enhancer_PaletteSave (SWI &42A52)<br>Enhancer_PaletteLoad (SWI &42A53)                      |                                       |  |

| <b>Related vectors</b> | None                                                                                        |                                       |  |

## \*ClearSave

|                  | Saves current extended palette mode screen as a CLEAR file                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax           | *ClearSave <filename></filename>                                                                                                                                                                                                                                                                                                              |

| Parameters       | <filename> is any valid filename</filename>                                                                                                                                                                                                                                                                                                   |

| Use              | *ClearSave is used to save the current extended palette mode screen<br>as a CLEAR file, using the file format used by the graphics utility !<br>Translator, by John Kortink, public domain versions of which are<br>available from a number of sources. The filetype of CLEAR files is<br>&690. See Appendix A for details of the file format |

| Example          | *ClearSave screenfile Saves the current screen as "screenfile"                                                                                                                                                                                                                                                                                |

| Related commands | *ClearLoad                                                                                                                                                                                                                                                                                                                                    |

| Related SWIs     | Enhancer_ClearSave (SWI &42A54)<br>Enhancer_ClearLoad (SWI &42A5C)                                                                                                                                                                                                                                                                            |

| Related vectors  | None                                                                                                                                                                                                                                                                                                                                          |

# \*ClearLoad

#### Loads CLEAR file to the screen

| Syntax                  | *ClearLoad <filename></filename>                                                                                                                                                                                                                                                                                   |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters              | <filename> is any valid filename</filename>                                                                                                                                                                                                                                                                        |

| Use                     | *Clearload is used to load a CLEAR file to the screen. It will change to the correct mode, program the extended palette, and load the image into screen memory. If the X & Y resolution of the CLEAR file image does not match that of any known mode, or the file does not use a palette, an error will be given. |

| Example                 | *ClearLoad screenfile Loads "screenfile" as image                                                                                                                                                                                                                                                                  |

| <b>Related commands</b> | *ClearS ave                                                                                                                                                                                                                                                                                                        |

| Related SWIs            | Enhancer_ClearSave (SWI &42A54)<br>Enhancer_ClearLoad (SWI &42A5C)                                                                                                                                                                                                                                                 |

| <b>Related vectors</b>  | None                                                                                                                                                                                                                                                                                                               |

# \*GreyScale

|                        | Sets extended palette to linear greyscale                                                                                                                          |                                           |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| Syntax                 | *GreyScale <0 1>                                                                                                                                                   |                                           |  |

| Parameters             | <0 1> is 0 for normal greyscale, 1 for reversed greyscale                                                                                                          |                                           |  |

| Use                    | *GreyScale is used to set the extended palette to a linear greyscale, either from black to white (normal, <n>=0), or from white to black (reversed,<n>=1).</n></n> |                                           |  |

| Example                | *GreyScale 0                                                                                                                                                       | Sets extended palette to normal greyscale |  |

| Related commands       | None                                                                                                                                                               |                                           |  |

| Related SWIs           | Enhancer_GreyScale (SWI &42A59)                                                                                                                                    |                                           |  |

| <b>Related vectors</b> | None                                                                                                                                                               |                                           |  |

#### \*Gcol

|                  | Sets graphics colour in extended palette modes.                                                                                                                                                  |                                        |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Syntax           | *Gcol <colour> [&lt;0 1&gt;]</colour>                                                                                                                                                            | [ <action]< th=""></action]<>          |  |

| Parameters       | <colour> is an 8-bit number<br/>[&lt;0 1&gt;] is 0 for foreground or 1 for background<br/>[<action>] is the standard GCOL action (see Archimedes BASIC<br/>manual for details)</action></colour> |                                        |  |

| Use              | *Gcol is used to set the foreground or background graphics colour in extended palette modes. It is the equivalent of the BASIC GCOL command.                                                     |                                        |  |

| Example          | *Gcol 100 0                                                                                                                                                                                      | Sets foreground graphics colour to 100 |  |

| Related commands | None                                                                                                                                                                                             |                                        |  |

| Related SWIs     | Enhancer_Colour (SWI &42A56)<br>Enhancer_Gcol (SWI &42A57)                                                                                                                                       |                                        |  |

| Related vectors  | None                                                                                                                                                                                             |                                        |  |

## \*Colour

|                  | Sets text colour in extend                                                                                                                   | led palette modes.                 |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Syntax           | *Colour <colour> [&lt;0 1&gt;</colour>                                                                                                       | ]                                  |

| Parameters       | <colour> is an 8-bit number<br/>[&lt;0 l&gt;] is 0 for foreground or I for background</colour>                                               |                                    |

| Use              | *Colour is used to set the foreground or background text colour in extended palette modes. It is the equivalent of the BASIC COLOUR command. |                                    |

| Example          | *Colour 200 0                                                                                                                                | Sets background text colour to 200 |

| Related commands | None                                                                                                                                         |                                    |

| Related SWIs     | Enhancer_Colour (SWI &42A56)<br>Enhancer_Gcol (SWI &42A57)                                                                                   |                                    |

| Related vectors  | None                                                                                                                                         |                                    |

## \*LinkMode

Loads mode description file and links it in as a screen mode.

| Syntax           | *LinkMode [ <filename>]</filename>                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameters       | [ <filename>] is any valid filename.</filename>                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Use              | *LinkMode is used to load a compiled MDL file, and to link it in so that it<br>can be used as a normal screen mode. If the MDL file does not have a valid<br>header, is the wrong size, or is the wrong filetype, an error will be given.<br>*LinkMode with no parameter will list the currently linked modes, giving<br>info on each. See Appendix D for details of the MDL mode block format. |  |  |

| Example          | *LinkMode mode22 Links file "mode22" as a screen mode.                                                                                                                                                                                                                                                                                                                                          |  |  |

| Related commands | *LinkModeClear<br>*DeLinkMode                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Related SWIs     | Enhancer LinkMode (SWI &42A5D)<br>Enhancer_LinkModeClear (SWI &42A5E)<br>Enhancer_DeLinkMode (SWI &42A5F)                                                                                                                                                                                                                                                                                       |  |  |

| Related vectors  | None                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

## \*LinkModeClear

|                  | Deletes all currently linked modes                                                                        |  |

|------------------|-----------------------------------------------------------------------------------------------------------|--|

| Syntax           | *LinkModeClear                                                                                            |  |

| Parameters       | None                                                                                                      |  |

| Use              | *LinkModeClear is used to delete all currently linked MDL modes.                                          |  |

| Example          | *LinkModeClear Clears all linked modes from memory.                                                       |  |

| Related commands | *LinkMode<br>*DeLinkMode                                                                                  |  |

| Related SWIs     | Enhancer_LinkMode (SWI &42A5D)<br>Enhancer_LinkModeClear (SWI &42A5E)<br>Enhancer_DeLinkMode (SWI &42A5F) |  |

| Related vectors  | None                                                                                                      |  |

#### \*DeLinkMode

#### Deletes individual linked mode

| Syntax                 | *DeLinkMode <val></val>                                                                                   |                              |

|------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------|

| Parameters             | <val> is the number of a linked mode.</val>                                                               |                              |

| Use                    | *DeLinkMode is used to delink a named linked MDL mode.                                                    |                              |

| Example                | *DeLinkMode 40                                                                                            | Removes mode 40 from memory. |

| Related commands       | *LinkMode<br>*LinkModeClear                                                                               |                              |

| Related SWIs           | Enhancer_LinkMode (SWI &42A5D)<br>Enhancer_LinkModeClear (SWI &42A5E)<br>Enhancer DeLinkMode (SWI &42A5F) |                              |

| <b>Related vectors</b> | None                                                                                                      |                              |

#### **\*TiffSave**

|                        | Saves current extended palette mode screen as a class P TIFF file                                                                                                                                                                             |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax                 | *TiffSave <filename></filename>                                                                                                                                                                                                               |  |  |

| Parameters             | <filename> is any valid filename</filename>                                                                                                                                                                                                   |  |  |

| Use                    | *TiffSave is used to save the current extended palette mode screen as a Class P TIFF file. The filetype of TIFF files is &FF0. See Appendix B, and the Aldus/Microsoft technical documentation on TIFF files, for details of the file format. |  |  |

| Example                | *TiffSave screenfile Saves the current screen as "screenfile"                                                                                                                                                                                 |  |  |

| Related commands       | None                                                                                                                                                                                                                                          |  |  |

| Related SWIs           | Enhancer_TiffSave (SWI &42A61)                                                                                                                                                                                                                |  |  |

| <b>Related vectors</b> | None                                                                                                                                                                                                                                          |  |  |

# \*Configure CrystalSlots

|                  | Configures occupied oscillator sockets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Syntax           | *Configure CrystalSlots <n></n>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |  |  |

| Parameters       | <n> is an 8-bit number</n>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |  |  |

| Use              | *Configure CrystalSlots is used to tell the system which of the available<br>oscillator sockets have oscillator modules in them. The 8-bit parameter is<br>treated in a bitwise fashion, ie. each bit represents a socket. If a bit is set to<br>1, it has an oscillator. The sockets which are always occupied, 0-3 & 7, are<br>masked out in software and cannot be changed. *Status shows the<br>configured sockets as a bit pattern. A socket which does not have an<br>oscillator in it should not be configured as occupied, as selecting it will<br>remove all clock signals from the VIDC, which will usually crash the<br>machine. |                            |  |  |

| Example          | *Configure CrystalSockets 2_10011111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Marks socket 4 as occupied |  |  |

| Related command: | *Clock<br>*Configure DefaultCrystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |  |  |

| Related SWIs     | Enhancer Clock (SWI &42A4C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |  |  |

| Related vectors  | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |  |  |

# \*Configure DefaultCrystal

|                  | Configures default VIDC clock                                                                                                                                                                                                                                                                                                                                                                                          |                                  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Syntax           | *Configure DefaultCrystal <n></n>                                                                                                                                                                                                                                                                                                                                                                                      |                                  |  |  |

| Parameters       | <n> is a number between 0 and 7</n>                                                                                                                                                                                                                                                                                                                                                                                    |                                  |  |  |

| Use              | *Configure DefaultCrystal is used to tell the system which of the available oscillator sockets is to be used as the default one. The default crystal will be used for modes which run at 24 MHz on a standard machine, hence a default crystal of 1 will run all 24 MHz modes at 25. 175 MHz. This setting is ignored if the monitor type is 0. A socket which is not marked as occupied cannot be set as the default. |                                  |  |  |

| Example          | *Configure DefaultCrystal 1                                                                                                                                                                                                                                                                                                                                                                                            | Sets socket 1 as the default one |  |  |

| Related commands | *Clock<br>*Configure CrystalSlots                                                                                                                                                                                                                                                                                                                                                                                      |                                  |  |  |

| Related SWIs     | Enhancer_Clock (SWI &42A4C)                                                                                                                                                                                                                                                                                                                                                                                            |                                  |  |  |

| Related vectors  | None                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |  |  |

# \*Configure ProcessorType

|                        | Configures installed processor type                                                                                                                                                                                                      |                                                                                              |                         |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|--|--|

| Syntax                 | *Configure ProcessorType <n></n>                                                                                                                                                                                                         |                                                                                              |                         |  |  |

| Parameters             | <n> is a number between 0 and 3</n>                                                                                                                                                                                                      |                                                                                              |                         |  |  |

| Use                    | *Configure ProcessorType is used to tell the system which of the various processor options is installed in the system. This is to keep internal timing loops running at the correct speed. The available processor types are as follows: |                                                                                              |                         |  |  |

|                        | 0                                                                                                                                                                                                                                        | An ARM2 running at 8 MHz, as in standard 300, 400, & . 400/1 series machines, and the A3000. |                         |  |  |

|                        | 1                                                                                                                                                                                                                                        | An ARM3 running at 8 MHz with a 20 MHz cache.                                                |                         |  |  |

|                        | 2                                                                                                                                                                                                                                        | An ARM3 running at 8 MHz with a 30 MHz cache.                                                |                         |  |  |

|                        | 3                                                                                                                                                                                                                                        | An ARM3 running at 12 MHz with a 30MHz cache. This i currently only the 540.                 |                         |  |  |

| Example                | *Configure                                                                                                                                                                                                                               | ProcessorType 2                                                                              | ARM3 upgrade at 30 MHz. |  |  |

| Related commands       | None                                                                                                                                                                                                                                     |                                                                                              |                         |  |  |